ne kontam pitanje, pa copy / paste ovoga u stm32duino okruzenje ce da radi ne mora menjas nista ako se ja dobro secam? ... nema bas niko dovoljno dokon al evo nesto na brzaka

Code:

RCC->APB2ENR|=RCC_APB2ENR_IOPAEN | RCC_APB2ENR_IOPBEN | RCC_APB2ENR_IOPCEN | RCC_APB2ENR_TIM1EN;

podesava rcc paraetre (Reset and Clock Control System) - pali klok na APB2 periferiji IOPA, IOPB, IOPC i TIMER1

Code:

GPIOA->CRH=SET_CRH(TIM1_CH1_PA,M_OUT_50M,OUT_AF_PP) | SET_CRH(TIM1_CH2_PA,M_OUT_50M,OUT_AF_PP);

GPIOB->CRH=SET_CRH(TIM1_CH1N_PB,M_OUT_50M,OUT_AF_PP);

GPIOC->CRH=SET_CRH(LED1_G_PC,M_OUT_50M,OUT_GP_PP) | SET_CRH(LED2_B_PC,M_OUT_50M,OUT_GP_PP);

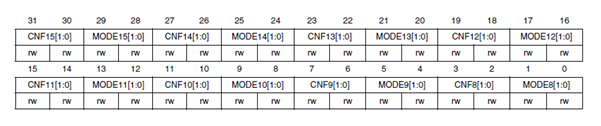

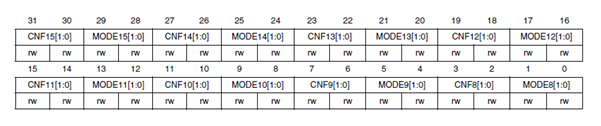

CRH je "gornjih 16 bitova", znaci postavlja za portove A, B i C pinove (gore su ti definisani koji su pinovi u #define delu) na 1

(source:

http://embedded-lab.com/blog/stm32-gpio-ports-insights/ )

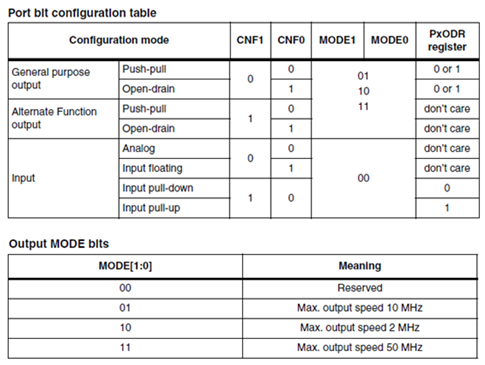

ovo ti je crh registar

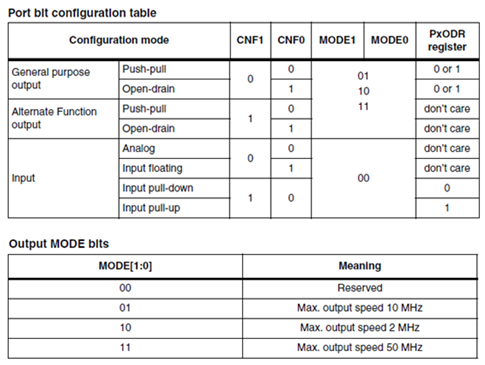

ovo ti je objasnjenje sadrzaja registra

Code:

//CH1: PWM mode 2, CH2: PWM mode 1, preload enabled on all channels

TIM1->CCMR1=TIM_CCMR1_OC1M_2 | TIM_CCMR1_OC1M_1 | TIM_CCMR1_OC1M_0 | TIM_CCMR1_OC1PE | TIM_CCMR1_OC2M_2 | TIM_CCMR1_OC2M_1 | TIM_CCMR1_OC2PE;

TIM1->CCER=TIM_CCER_CC1E | TIM_CCER_CC2E;

TIM1->BDTR=TIM_BDTR_MOE;

TIM1->CCR1=TMR_T - PWM_VALUE;

TIM1->CCR2=PWM_VALUE;

TIM1->ARR=TMR_T;

TIM1->CR1=TIM_CR1_ARPE | TIM_CR1_CMS_1 | TIM_CR1_CMS_0;

TIM1->CR1|=TIM_CR1_CEN;

TIM1->EGR=TIM_EGR_UG;

pise gore u komentaru, pali pwm1 na mode 2, pwm2 na mode1 pali u pokrece iste

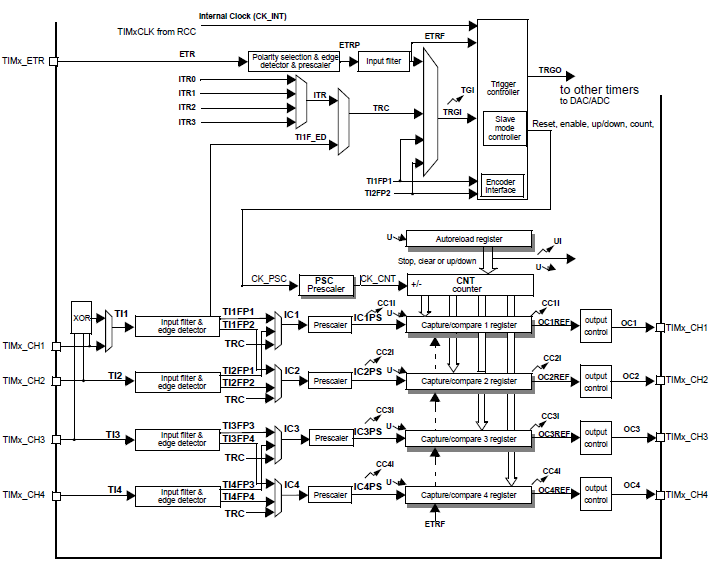

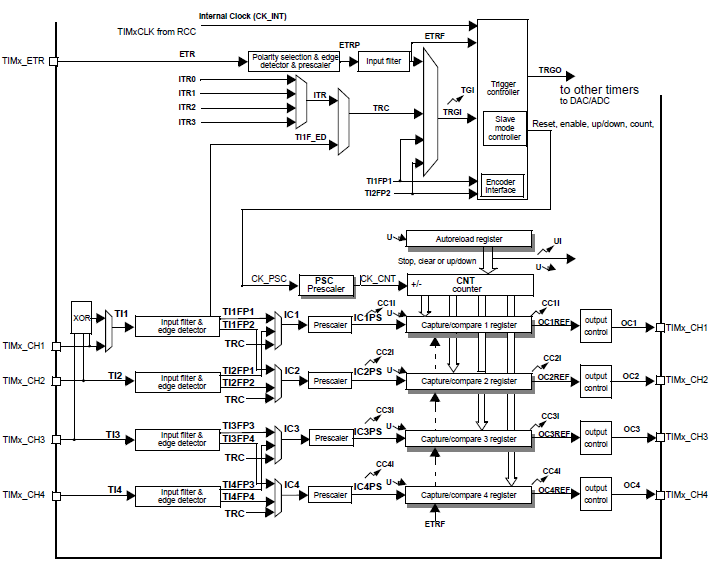

imas ovde semu tajmera ( source:

http://embedded-lab.com/blog/stm32-timers/ )

inace iz

http://www.st.com/content/ccc/...translations/en.DM00042534.pdf

Citat:

The timer is able to generate PWM in edge-aligned mode or in center-aligned mode with a frequency determined by the value of the TIMx_ARR register, and a duty cycle determined by the value of the TIMx_CCRx register.

PWM mode 1

• In up-counting, channelx is active as long as CNT< CCRx, otherwise it is inactive.

• In down-counting, channelx is inactive as long as CNT> CCRx, otherwise it is active.

PWM mode 2

• In up-counting, channelx is inactive as long as CNT < CCRx, otherwise it is active.

• In down-counting, channelx is active as long as CNT > CCRx, otherwise it is inactive.

Note:

Active when OCREF = 1, inactive when OCREF = 0.

To configure the timer in this mode:

1. Configure the output pin:

a) Select the output mode by writ ing CCS bits in CCMRx register.

b) Select the polarity by writing the CCxP bit in CCER register.

2. Select the PWM mode (PWM1 or PWM2) by writing OCxM bits in CCMRx register.

3. Program the period and the duty cycle respectively in ARR and CCRx registers.

4. Set the preload bit in CCMRx register and the ARPE bit in the CR1 register.

5. Select the counting mode:

a) PWM edge-aligned mode: the counter must be configured up-counting or down-counting.

b) PWM center aligned mode: the counter mode must be center aligned counting mode (CMS bits different from '00').

6. Enable the capture compare.

7. Enable the counter.

u svakom slucaju savet je mani se arduina, skini atolic true studio (sad se zove valjda stm32 true studio), full je ide i free je i radi do jaja sa stm32, skini cubemx, tamo lepo nacrtas sta oces i on ti izgenerise sve ovo ... ako vec neces da citas sta je koji registar onda klikci i zaobidji stm32duino

STM32F103 push pull i AVR (atmega168) push pull

STM32F103 push pull i AVR (atmega168) push pull